處理器(qì)係統 | ● DSP+CPU 雙核架構(gòu) ● CPU:32 位 RISC 處(chù)理器,ARMv7-M 指令集結構,1.2 DMIPS/MHz,主頻(pín) 200MHz ● DSP:8-way 的超級流水線結構,4 個 ALU(2 個 40bit、2 個 16bit),2個 MAU(4 個 16x16bit macs),1.5 DMIPS/MHz,主頻 200MHz ● 獨立的(de)高(gāo)性能多通道(dào) DMA,支持外設與存(cún)儲間的數(shù)據傳輸 |

外圍接口 | ●1 個 RMII 接口,支持 10/100Mbit/s網絡擴展(zhǎn) ●1 個獨立的 SPI FLASH 接口 ●2 個(gè) SPI 接口、2 個 I2C 接口(kǒu)、5 個 UART 接口、2 個(gè)紅外(wài)接口、1 個 RMII接口、1 個 QSPI-SPRAM 接口, 50 個 GPIO 接口、4 路 PWM ●1 路 AD 輸入(16bit,3 通道) |

安全設備 | ●支持 AES-128/192/256 加密/解密(mì)協處理器 ●支持 EFUSE,容量為 512bit,軟(ruǎn)件可(kě)隨機或連續讀取 ●支持 IEEE 802.3 中(zhōng) CRC-32/CRC-24 循(xún)環算法引擎 |

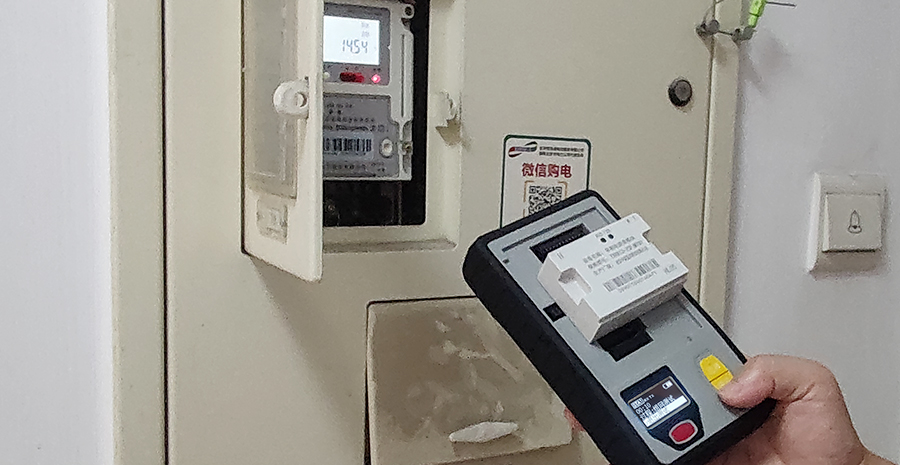

標準和協議 | ●支持 2017國網和南網HPLC載波(bō)通信標準 ●支持G3-PLC標準,支持(chí)窄帶(dài)標準 ● 智能電網協議標準* |

通信(xìn)指標(biāo) | ●物(wù)理層峰值速率 12Mbit/s ●接收靈敏度優於-108dBm |

物理層特性 | ●支持 2018 國家電網和南方電網載波通信標準。對同樣使用該標準子集芯片,能實現互聯互通(tōng) ●支持 150K 以下、150K~500K、1.953MHz~11.96MHz、2.441MHz~5.615MHz、0.781MHz~2.930MHz、1.758MHz~2.930MHz 等多種頻段,子載波(bō)可配置 ●采(cǎi)用(yòng) OFDM 技術,支持 DBPSK、DQPSK、D8PSK、BPSK、QPSK、16QAM等調製模式 ●支持(chí) FEC(Turbo/Viterbi/RS)和 CRC 功(gōng)能,強大的去噪和糾錯能力 |

組網特性 | ●支持自組網和動態多路(lù)由尋址(zhǐ)功能 |

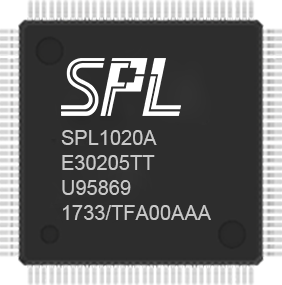

其他 | ●工藝:SMIC40nm LL ●封裝:14x14mm 128-pin QFP,8x8mm 68-pin QFN ●工作溫度:-40℃~+85℃ ●工作電壓:3.3V、1.1V |

*備注:智能電網協議標(biāo)準未(wèi)凍結,其他技術標準可選,對同樣使用該(gāi)標準(zhǔn)子集(jí)芯片,能實現互聯互(hù)通。